# AN10960 DALI slave using the LPC1112 Rev. 1 — 22 July 2010

**Application note**

### **Document information**

| Info     | Content                                                                                                                                                                   |  |  |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Keywords | LPC1112, Cortex M0, UBA2014, DALI slave unit, HFTL ballast                                                                                                                |  |  |

| Abstract | This application note describes the design of a DALI (Digitally Addressable Lighting Interface) slave unit, based on the LPC1112 microcontroller from NXP Semiconductors. |  |  |

# **DALI slave using the LPC1112**

# **Revision history**

| Rev | Date     | Description      |

|-----|----------|------------------|

| 01  | 20100722 | Initial revision |

# **Contact information**

For additional information, please visit: <a href="http://www.nxp.com">http://www.nxp.com</a>

For sales office addresses, please send an email to: <a href="mailto:salesaddresses@nxp.com">salesaddresses@nxp.com</a>

**DALI slave using the LPC1112**

## 1. Introduction

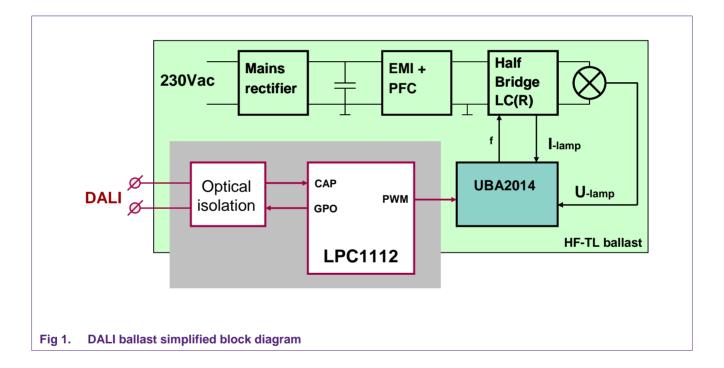

This report describes the design of a DALI (Digitally Addressable Lighting Interface) slave unit, based on the LPC1112 from NXP Semiconductors. It illustrates how to add DALI functionality to an existing HF-TL dimmable ballast design. In that case, the complete (DALI ballast) application (see Fig 1) contains two main parts:

- 1. The ballast control section, based on a UBA2014 (not discussed in this app. note)

- 2. The DALI slave control section, based on an LPC1112

The communication between the ballast and the external world is done with just two signals (Tx and Rx), allowing the ballast to communicate bi-directional with the DALI system network. An optical isolated digital interface assures high voltage isolation between the DALI inputs and the lamp output stage.

# 1.1 DALI protocol

The international standard (IEC 60929) DALI-bus communication protocol is intended for use in digital TL-ballast intelligent lighting systems. In a typical application, a DALI-bus consists of one controller (master), and multiple slave units (normally TL-ballasts). It can control up to 64 different slaves (ballasts) within the same control system. It's possible to transmit commands to single ballasts or to a group of ballasts.

For electrical bus specification please refer to the international standard. For DALI command protocol, addressing modes and specific protocol timing requirements, see NXP application note AN10760 (see <u>References</u>).

# **DALI slave using the LPC1112**

### 1.2 DALI Ballast

Ballasts are able to have 1 short address, 16 group addresses and will also react to broadcast commands. Additionally, they are able to store 16 scenes, a fade rate, a fade time, and MIN-, MAX-, POWER-ON and SYSTEM FAILURE levels.

Al these parameters (constants) are stored in persistent (flash) memory and can be changed by the master. <u>Table 1</u> gives a complete overview of the DALI ballast constants, variables and their default or 'factory' programmed values.

Table 1. DALI ballast declaration of variables

| Variable             | Default value       | Reset value     | Range                | Memory type          |

|----------------------|---------------------|-----------------|----------------------|----------------------|

| Actual Dim Level     | not applicable      | 254             | 0, min – max         | 1 byte RAM           |

| Power On Level       | 254                 | no change       | 1 – 254              | 1 byte Flash (IAP)   |

| System Failure Level | 254                 | no change       | 0 – 255 (mask)       | 1 byte Flash (IAP)   |

| MIN Level            | Physical MIN Level  | no change       | Phys MIN – MAX Level | 1 byte Flash (IAP)   |

| MAX Level            | 254                 | no change       | MIN Level – 254      | 1 byte Flash (IAP)   |

| Fade Rate            | 7 (45 steps/sec)    | no change       | 1 – 15               | 1 byte Flash (IAP)   |

| Fade Time            | 0 (no fade)         | no change       | 0 – 15               | 1 byte Flash (IAP)   |

| Short Address        | 255 (no address)    | no change       | 0 - 63, 255 (mask)   | 1 byte Flash (IAP)   |

| Search Address       | 0xFFFFFF            | 0xFFFFFF        | 0 – 0xFFFFFF         | 3 bytes RAM          |

| Random Address       | 0xFFFFFF            | no change       | 0 – 0xFFFFFF         | 3 bytes Flash (IAP)  |

| Group 0 - 7          | 00000000 (no group) | no change       | 0 – 255              | 1 byte Flash (IAP)   |

| Group 8 - 15         | 00000000 (no group) | no change       | 0 – 255              | 1 byte Flash (IAP)   |

| Scene 0 - 15         | 16 x 255 (mask)     | no change       | 16 x 0 – 255 (mask)  | 16 bytes Flash (IAP) |

| Status Info          | not applicable      | 0?100???        | 0 – 255              | 1 byte RAM           |

| Version Number       | Factory burn-in     | Factory burn-in | 0 – 255              | 1byte Flash          |

| Physical Min Level   | Factory burn-in     | Factory burn-in | 1 – 254              | 1 byte Flash         |

### 1.3 Frame structure

The ballast operates in a master-slave mode where the ballast is the slave and any control unit is the master. A command sent by the master is called a "forward frame" and consists of bi-phase coded bits: 1 start bit (logical '1'), 1 address byte, 1 data byte and 2 stop bits (idle). An answer from the ballast (slave), called a "backward frame" shall consist of bi-phase coded bits: 1 start bit (logical '1'), 1 data byte and 2 stop bits (idle).

The frame structure is tested in the receiving unit. In case of code violation the frame is ignored. 1.7 ms after the occurrence of a code violation the ballast must be ready again for data reception. Query commands from the master are of the kind that they can be answered with 'Yes', 'No' or 8-bit information. The answers (backward frames) are:

• 'Yes': 1111 1111

'No': The ballast does not react (sends nothing)'

• 8-bit information: XXXX XXXX

### **DALI slave using the LPC1112**

# 1.4 Addressing DALI ballasts

When leaving the factory ballasts have no short and no group address assigned (see <u>Table 1</u>). So, after a DALI system installation, the master first needs to allocate a short address to each individual slave. There are two ways to do this:

### Random addressing

- The master sends the INITIALIZE command, which enables the next addressing commands for 15 minutes

- 2. The master sends the RANDOMIZE command to make each ballast generate a 24-bit random number (stored flash in RANDOM\_ADDRESS)

- 3. The master searches the ballast with the lowest random number using Search Address and the COMPARE command

- 4. The found ballast gets a unique (6-bit) short address (stored in flash), with command: PROGRAM SHORT ADRESS

- 5. Verify the programmed short address with VERIFY SHORT ADDRESS command

- 6. This ballast is removed from the search process by WITHDRAW command

- 7. This procedure is repeated until all ballasts have a short address.

- 8. The process is stopped by the TERMINATE command

### **Physical Selection addressing**

- 1. The master sends command INITIALISE

- 2. The master sends command PHYSICAL SELECTION

- 3. The master repeats command QUERY SHORT ADDRESS periodically until a ballast replies (this ballast is physically selected)

- The master sends command PROGRAM SHORT ADDRESS containing the ballast's address.

- The master sends RECALL MIN LEVEL and RECALL MAX LEVEL using the short address for optical feedback for some seconds

- 6. Steps 2 to 5 are repeated for all ballasts

# 1.5 Data Transfer Register

The Data Transfer Register (DTR) is an 8-bit memory location of the ballast (in SRAM) to store temporary data from the master (using command DATA TRANSFER REGISTER). After that, other commands are used to move the contents of the DTR to specific parameters (for example command STORE DTR AS SHORT ADDRESS).

### 1.6 Ballast operation

Some operational specifications for DALI ballasts are:

### **Power On**

The DALI commands (from master) are received properly 0.5 sec after 'Power-On'. Earliest after another 100 ms the ballast will go to the predefined 'POWER-ON LEVEL'

# **DALI slave using the LPC1112**

via preheat- and ignition phase (if applicable). During the 100 ms interval the ballast shall react on a possible command if this 'POWER-ON LEVEL' is not desired.

## **Logarithmic Dimming Curve**

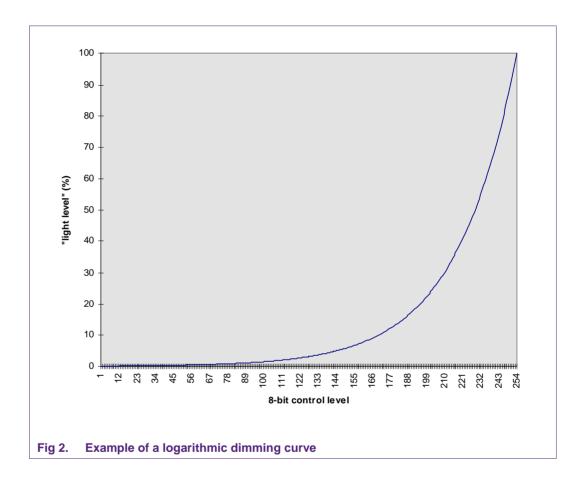

The lowest dimming level of the ballast is 0.1 % and is coupled to the digital value '1' in the range of 1 to 254 (absolute dimming). The highest arc power level of the ballast (100 %) is coupled to the digital value '254'. A logarithmic dimming curve from 0.1 % to 100 % is defined (see Fig 2). Because of the many different influences, dim levels can only have the meaning of arc power level of a lamp.

### **Min and Max Control Level**

Programming a MIN level above or a MAX level below the actual power level will set the actual power level to the new MIN level or MAX level. Programming a MIN level below or a MAX level above the actual power level will not affect the actual arc power level.

A required level below the MIN level or above the MAX level will cause the ballast to operate at MIN LEVEL or MAX LEVEL.

The arc power levels '0' (OFF) and '255' (MASK) shall not be affected by the MIN and MAX LEVEL settings.

# **DALI slave using the LPC1112**

### **Fade Time and Fade Rate**

Some power control commands use the actual Fade Time (see <u>Table 1</u>) constant to dim up/down to the required light level. The Fade Time constant can have a value from 0 to 15 that corresponds to a defined time in seconds (see <u>Table 2</u>).

Some power control commands use the actual Fade Rate (see <u>Table 1</u>) constant to dim up/down, during 200 milliseconds, to a new light level. The Fade Rate constant can have a value from 1 to 15 that will correspond to a defined number of (level) steps per second (see <u>Table 2</u>).

Table 2. Fade Time and Fade Rate

| FADE_TIME / FADE_RATE | Fade Time (sec) | Fade Rate (steps/sec) |

|-----------------------|-----------------|-----------------------|

| 0                     | 0               | not applicable        |

| 1                     | 0.707           | 357.796               |

| 2                     | 1.000           | 253.000               |

| 3                     | 1.414           | 178.898               |

| 4                     | 2.000           | 126.500               |

| 5                     | 2.828           | 89.449                |

| 6                     | 4.000           | 63.250                |

| 7                     | 5.657           | 44.725                |

| 8                     | 8.000           | 31.625                |

| 9                     | 11.314          | 22.362                |

| 10                    | 16.000          | 15.813                |

| 11                    | 22.627          | 11.181                |

| 12                    | 32.000          | 7.906                 |

| 13                    | 45.255          | 5.591                 |

| 14                    | 64.000          | 3.953                 |

| 15                    | 90.510          | 2.795                 |

### Scene 1 to 16

Ballasts can have 16 pre-defined light levels (stored in flash/eeprom) called 'scenes' (see <u>Table 1</u>). Command GO TO SCENE is used to set the actual arc power level of the ballast to the value stored for scene 1 to 16 using the actual fade time. If the ballast does not belong to the scene, the arc power level remains unchanged. If the lamp is off it will be ignited with this command.

# 2. Hardware

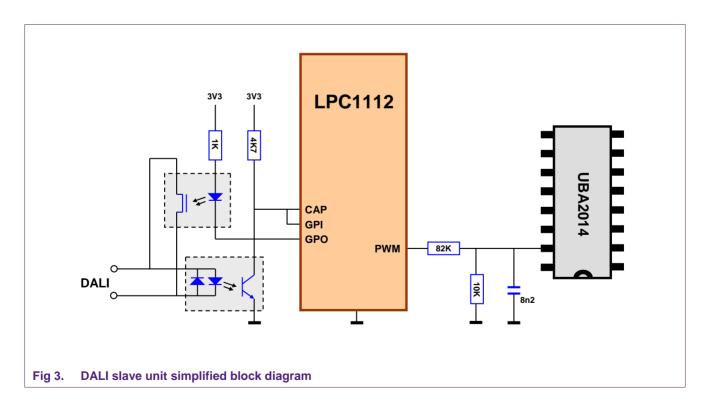

The DALI slave unit described in this application note is based on a low power and low cost LPC1112 microcontroller with an ARM Cortex M0 core (see Fig 3).

It uses timer CT32B1, match MAT0 output, to generate a PWM signal, with a variable duty cycle, that represents the lamp light level. The PWM signal is connected to the UBA2014 ballast controller to perform the actual dimming of the lamp. The UBA2014 hardware description is not part of this application note. For more information see application note AN10181 (see References).

# **DALI slave using the LPC1112**

To receive DALI commands, general purpose timer CT32B0, capture CAP0 input (P1.5) is used (capture and interrupt on both edges). The CAP0 pin is also connected to GPIO pin P2.6. This is needed to check high / low level (rising / falling edge) by software.

To send DALI slave backward frames again timer CT32B0 is used to control general purpose output pin (P2.0) as the DALI send signal.

# 2.1 Memory usage

The LPC1112 has a total of 16 kB of on-chip flash divided into four sectors of 4 kB. Code size used by the complete example application is ~6 kB (sector 0 and 1). Sector 2 is not used (free for software expansion). Sector 3 (starting at address 0x3000) is used to store the DALI ballast variables (only 28 bytes used). These are updated using IAP calls.

### 2.2 DALI interface

The DALI hardware bus driver logic (including the optical isolation) is not handled in detail in this application note.

# 2.3 Power supply

In the example application the LPC1112 runs at a CCLK of 2 MHz, derived from the onchip IRC of 12 MHz. If there's no DALI communication active, the LPC1112 will enter "SLEEP" mode. In this case the average current consumption is less than 1.3 mA (Idd). This means a cheap bleeder resistor or a simple capacitive divider could be used to supply the LPC1112.

**DALI slave using the LPC1112**

# 3. Software

# 3.1 Transmitting a DALI message

Sending a frame is relatively easy, see *dali\_drv.c* module. The implementation uses Timer 0 interrupt every period 'TE' to generate the DALI message. Sending a single bit via bi-phase encoding requires two interrupts, in order to produce a good transition. A '1' is sent by pulling down the line for one period, followed by releasing it for one period. Sending a '0' is exactly the opposite. A position counter is used to keep track of which bit is being transmitted. The counter runs at twice the bit frequency (just like the interrupt), so bit 0 can be used to detect whether the first or the second period of this bit is to be transmitted.

# 3.2 Decoding a DALI message

The best method to decode DALI (Manchester coding) messages is to detect the edges of the signal and measure the time between these edges. Using a timer capture input of the LPC1112 this is easy to accomplish, because the input can capture and generate an interrupt at both rising and falling edge. At the falling edge the pulse 'high time' is captured and stored. At a rising edge the pulse 'low time' is captured, and the received bit(s) is decoded. There are no separate interrupts for rising and falling edge input capture, and it's not possible to read the logic level of the capture input pin. That's why the capture input pin is also connected to a GPIO input pin.

### 3.3 Structure

The DALI slave unit software example is written in C language and compiled using Keil's uVision (ARM7 RealView, V4.12) free demo compiler. It performs the following main tasks:

- Initialization:

- for LPC1112 microcontroller configuration the standard startup code (see startup\_LPC11xx.s and system\_LPC11xx.c) from Keil were used and set as CCLK = IRC / 6 = 2 MHz

- DALI slave stack:

- DALI Driver: use Timer 0 match 0 for sending DALI forward frames. Use timer 0 capture 0 to receive DALI backward frames (see dali\_drv.c)

- DALI Command: for decoding and execution of the received DALI commands (see dali\_cmd.c)

- Application (3 modules):

- Main: handles 'sleep' mode, check and clear DALI transmission event flags and take action (see main.c)

- Ballast: handles dimming, fading and translation of required lamp light level into actual PWM duty cycle. It uses the 10 ms Systick Timer and timer CT32B1 match MAT0, to generate the PWM output signal (see ballast.c).

- FLASH: handles the storage of the DALI slave unit parameters, like MIN/MAX light levels, Addresses and scene's, using the on-chip flash of the LPC1112 (see flash.c).

# **DALI slave using the LPC1112**

# 4. References

For further details please refer to the following publications:

Datasheets / User Manuals / Application Notes / Example code:

http://ics.nxp.com/microcontrollers/

AN10181: "36W TLD application with the UBA2014":

http://www.nxp.com/documents/user\_manual/UM10389.pdf

AN10760: "DALI Master Using the LPC2141"

http://www.standardics.nxp.com/support/documents/microcontrollers/zip/an10760.zip

• Example Programs:

http://www.keil.com/download/

# **DALI slave using the LPC1112**

# 5. Legal information

### 5.1 Definitions

Draft — The document is a draft version only. The content is still under internal review and subject to formal approval, which may result in modifications or additions. NXP Semiconductors does not give any representations or warranties as to the accuracy or completeness of information included herein and shall have no liability for the consequences of use of such information.

### 5.2 Disclaimers

Limited warranty and liability — Information in this document is believed to be accurate and reliable. However, NXP Semiconductors does not give any representations or warranties, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information.

In no event shall NXP Semiconductors be liable for any indirect, incidental, punitive, special or consequential damages (including - without limitation - lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges) whether or not such damages are based on tort (including negligence), warranty, breach of contract or any other legal theory.

Notwithstanding any damages that customer might incur for any reason whatsoever, NXP Semiconductors' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Terms and conditions of commercial sale of NXP Semiconductors.

Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof.

Suitability for use — NXP Semiconductors products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an NXP Semiconductors product can reasonably be expected to result in personal injury, death or severe property or environmental damage. NXP Semiconductors accepts no liability for inclusion and/or use of NXP Semiconductors products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

**Applications** — Applications that are described herein for any of these products are for illustrative purposes only. NXP Semiconductors makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification.

Customers are responsible for the design and operation of their applications and products using NXP Semiconductors products, and NXP Semiconductors accepts no liability for any assistance with applications or

customer product design. It is customer's sole responsibility to determine whether the NXP Semiconductors product is suitable and fit for the customer's applications and products planned, as well as for the planned application and use of customer's third party customer(s). Customers should provide appropriate design and operating safeguards to minimize the risks associated with their applications and products.

NXP Semiconductors does not accept any liability related to any default, damage, costs or problem which is based on any weakness or default in the customer's applications or products, or the application or use by customer's third party customer(s). Customer is responsible for doing all necessary testing for the customer's applications and products using NXP Semiconductors products in order to avoid a default of the applications and the products or of the application or use by customer's third party customer(s). NXP does not accept any liability in this respect.

**Export control** — This document as well as the item(s) described herein may be subject to export control regulations. Export might require a prior authorization from national authorities.

**Evaluation products** — This product is provided on an "as is" and "with all faults" basis for evaluation purposes only. NXP Semiconductors, its affiliates and their suppliers expressly disclaim all warranties, whether express, implied or statutory, including but not limited to the implied warranties of non-infringement, merchantability and fitness for a particular purpose. The entire risk as to the quality, or arising out of the use or performance, of this product remains with customer.

In no event shall NXP Semiconductors, its affiliates or their suppliers be liable to customer for any special, indirect, consequential, punitive or incidental damages (including without limitation damages for loss of business, business interruption, loss of use, loss of data or information, and the like) arising out the use of or inability to use the product, whether or not based on tort (including negligence), strict liability, breach of contract, breach of warranty or any other theory, even if advised of the possibility of such damages.

Notwithstanding any damages that customer might incur for any reason whatsoever (including without limitation, all damages referenced above and all direct or general damages), the entire liability of NXP Semiconductors, its affiliates and their suppliers and customer's exclusive remedy for all of the foregoing shall be limited to actual damages incurred by customer based on reasonable reliance up to the greater of the amount actually paid by customer for the product or five dollars (US\$5.00). The foregoing limitations, exclusions and disclaimers shall apply to the maximum extent permitted by applicable law, even if any remedy fails of its essential purpose.

### 5.3 Trademarks

Notice: All referenced brands, product names, service names and trademarks are property of their respective owners.

11 of 12

# **DALI slave using the LPC1112**

# 6. Contents

| 1.  | Introduction                | 3  |

|-----|-----------------------------|----|

| 1.1 | DALI Protocol               | 3  |

| 1.2 | DALI Ballast                | 4  |

| 1.3 | Frame structure             | 4  |

| 1.4 | Addressing DALI ballasts    | 5  |

| 1.5 | Data Transfer Register      | 5  |

| 1.6 | Ballast operation           | 5  |

| 2.  | Hardware                    | 7  |

| 2.1 | Memory usage                | 8  |

| 2.2 | DALI interface              |    |

| 2.3 | Power supply                | 8  |

| 3.  | Software                    | 9  |

| 3.1 | Transmitting a DALI message | 9  |

| 3.2 | Decoding a DALI message     |    |

| 3.3 | Structure                   |    |

| 4.  | References                  | 10 |

| 5.  | Legal information           | 11 |

| 5.1 | Definitions                 |    |

| 5.2 | Disclaimers                 | 11 |

| 5.3 | Trademarks                  |    |

| 6   | Contents                    | 12 |

Please be aware that important notices concerning this document and the product(s) described herein, have been included in the section 'Legal information'.

© NXP B.V. 2010.

All rights reserved.